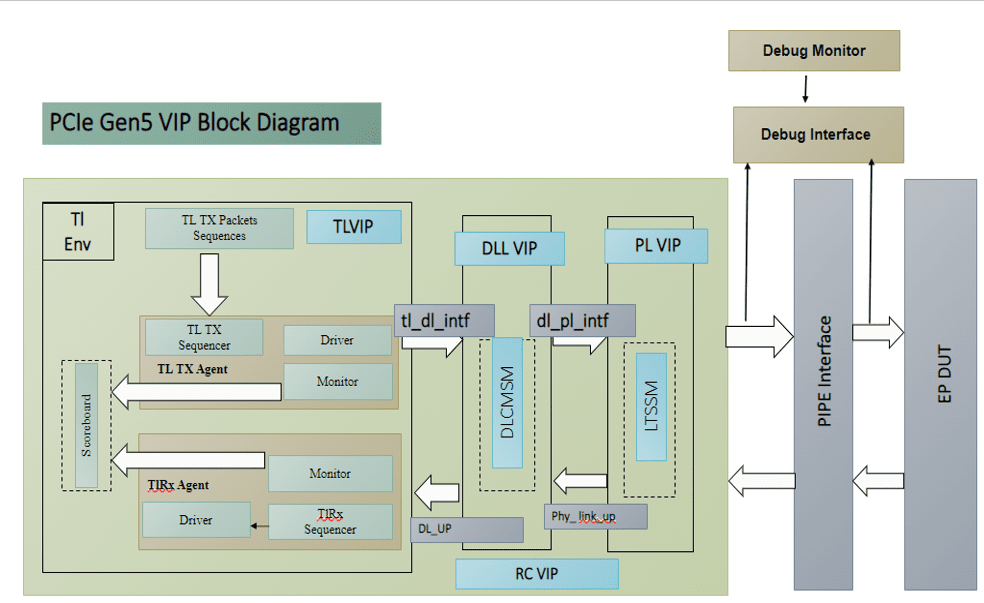

Simulus PCIe Gen5 VIP

Features:

- Compatibility : Adheres to conventional PCI software model for seamless integration.

- Transceivers: Utilizes GTH transceivers at 2.5 GT/s, 5.0 GT/s, and 8.0 GT/s for versatile data speeds.

- Lane Configuration: Configurable for 1, 2, 4, or 8 lanes, allowing tailored setups.

- Configuration Options: Supports Endpoint and Root Port configurations for system adaptability.

- I/O Virtualization: Enables multiple functions and SR-IOV for up to two physical and six virtual functions.

- Error Handling: Implements ECRC for data integrity and AER for advanced error reporting.

- User Interface: Standardized interfaces for straightforward integration with diverse system components.

- AXI4-Stream Compliance : Meets AXI4-Stream standards for efficient and consistent data transfer.

- Flow Control: Facilitates flow control of data and transaction discontinuation for efficient transmission.

- Power Management: Compliant with PCI and PCI Express power management functions for energy efficiency.

- Transaction Payload: Accommodates a maximum payload of up to 1024 bytes for large-scale data transfers.

- Error Handling: Implements ECRC for data integrity and AER for advanced error reporting.

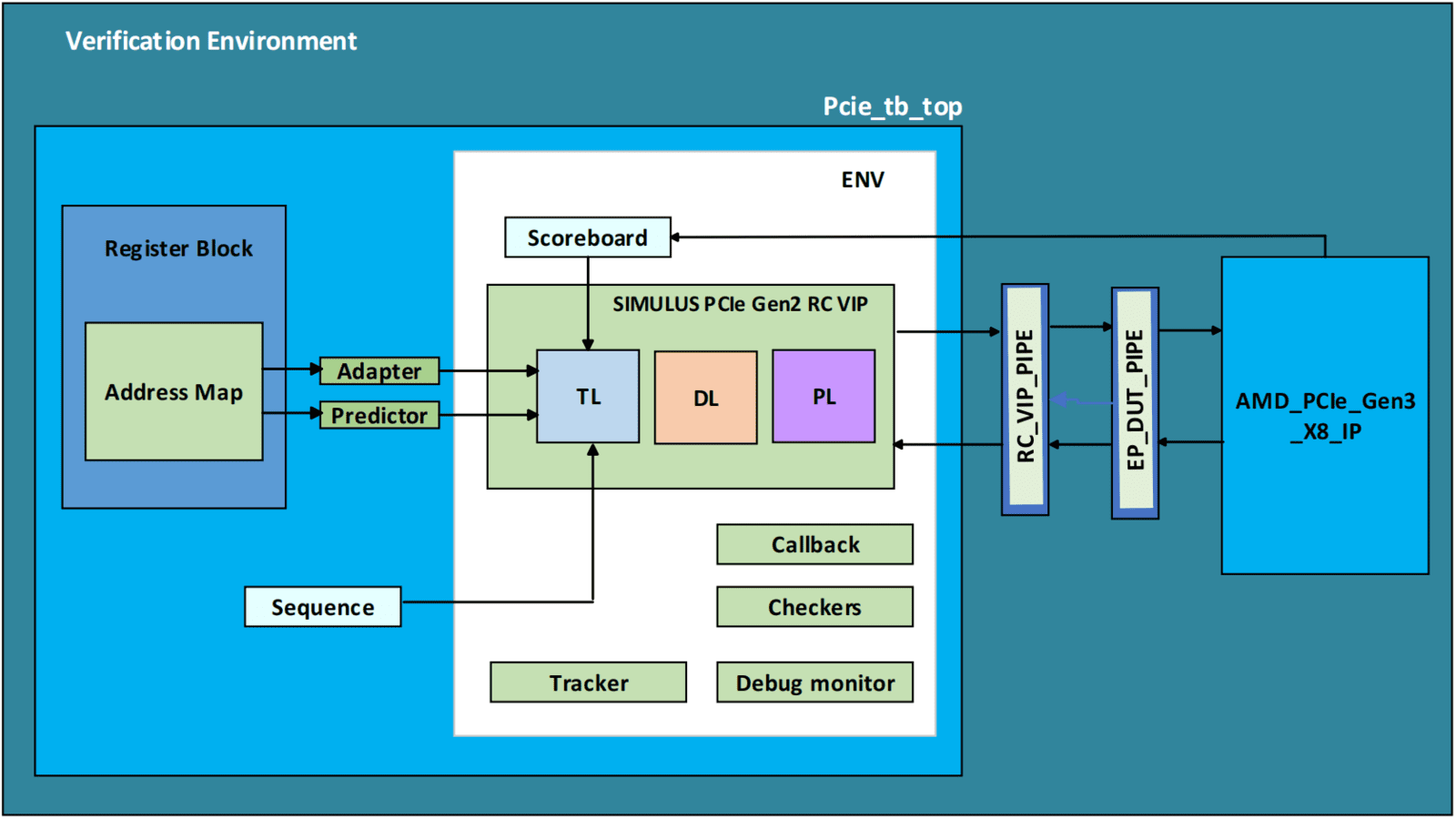

AMD_PCIe_Gen3_X8_IP Interop with Simulus PCIe Gen2 VIP

Features:

-

Comprehensive Implementation: The CXL Component Register Set IP meticulously implements the entire CXL component register set, ensuring compatibility and adherence to the CXL specification.

-

Wide Range of CXL Device Support: The IP supports a broad spectrum of CXL device types, including processors, memory devices, accelerators, and adapters, catering to diverse system configurations.

-

Efficient and Scalable Design: The IP is designed for efficiency and scalability, minimizing resource utilization while supporting complex CXL device configurations.

-

CXL Specification Compliance: The IP adheres strictly to the CXL specification, ensuring compatibility with various CXL implementations and promoting interoperability.

-

Seamless Integration: The IP seamlessly integrates with various system architectures, enabling straightforward adoption of CXL technology in different computing platforms.

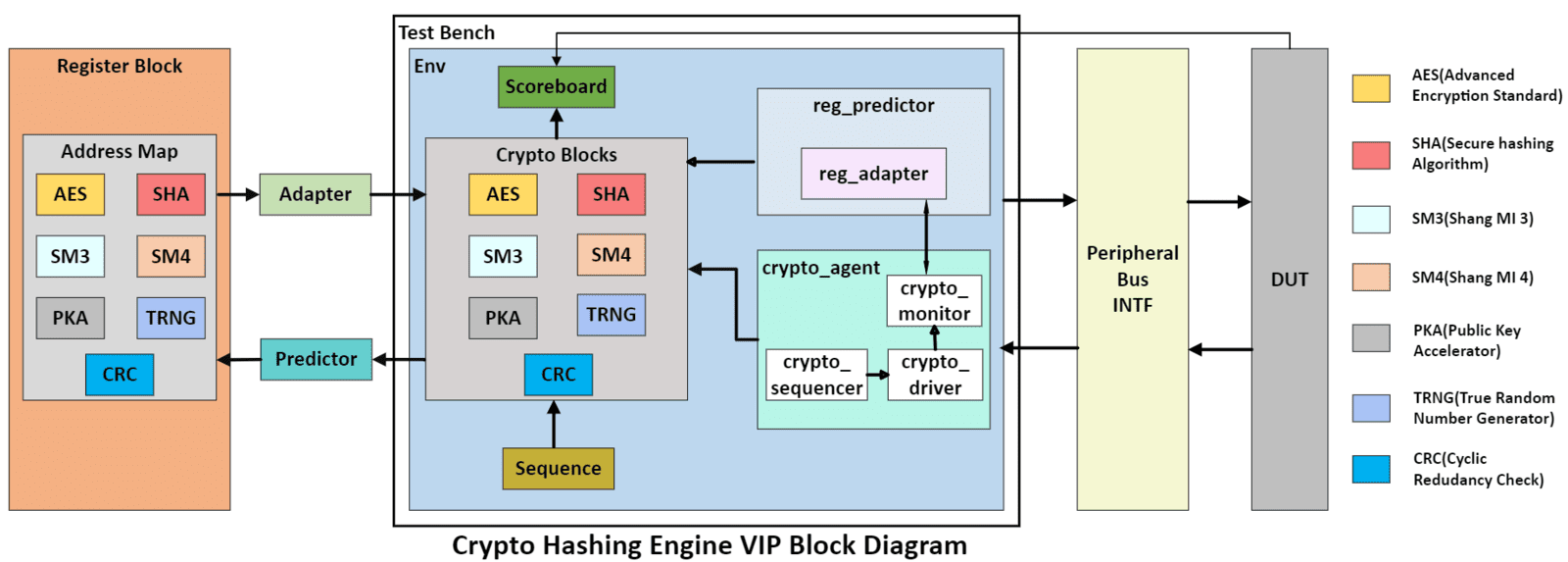

Crypto Hashing Engine VIP

Features:

- The block size is 128 bit for AES and SM4, 512 bit for SHA2-256, and 1024 bits for SHA2-512.

- EIP58T (SHA engine) and EIP38T (AES) support two contexts, they are often referred to as Secure (SHIB) and Public (P-HIB).

- AES, SHA and CRC IPs in DTHE support two contexts, namely Public and Secure with separate MMRs. The PKA, TRNG, SM3, and SM4 do not support dual contexts.

- The AES IP looks at the address and the secure input at the DTHE level.

- The SHA and CRC IP only looks at the address for the context access and it ignores the secure pin.

- It is expected that there is a firewall outside DTHE to protect MMR access in general.

- The DTHE_v2 module supports CBA4 VBUSP interface. The Crypto IPs internally use OCP, AHB or simple TCM interface, hence protocol conversion bridge or gasket is used.

- The purpose this engine is to accelerate CRC and TCP checksum operation.

- The result of the operation is a 32/16 or 8-bit signature which can be used to check the sanity of data

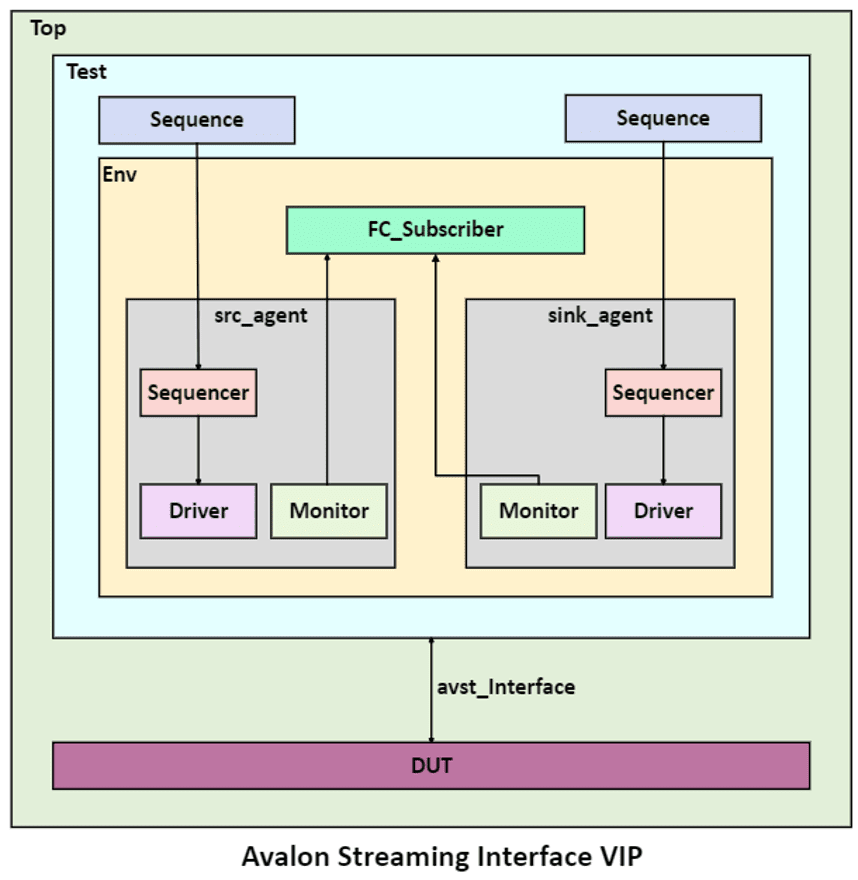

Avalon Streaming Interface VIP

Features:

- Low-latency, high-throughput point-to-point data transfer.

- Multiple channels support with flexible packet interleaving.

- Sideband signaling of channel, error, and start and end of packet delineation.

- Support for data bursting.

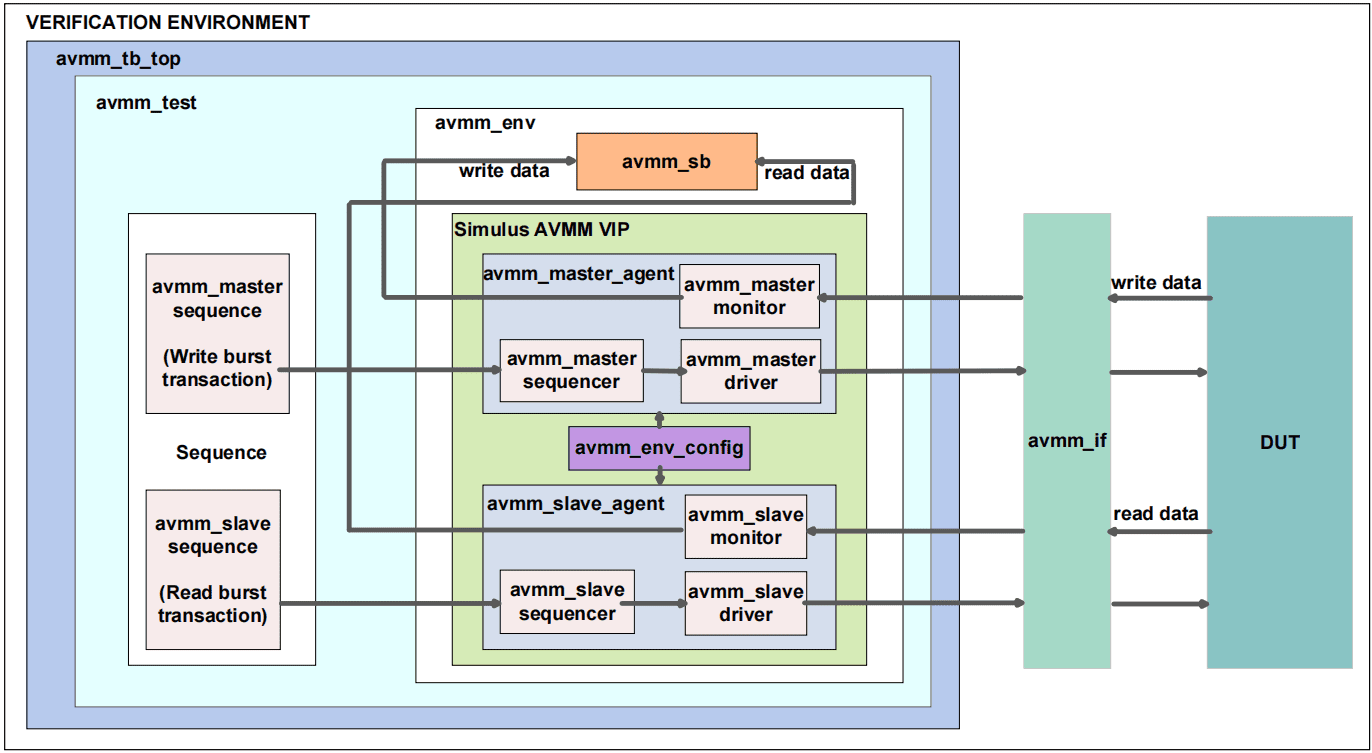

Avalon Memory Mapped Interface VIP

Features:

- Burst Transfer Generation.

- Random Data Generation.

- Master and Slave Agent Support.

- Monitor Integration.

- Scoreboard-based Verification.

- Customizable Parameters.

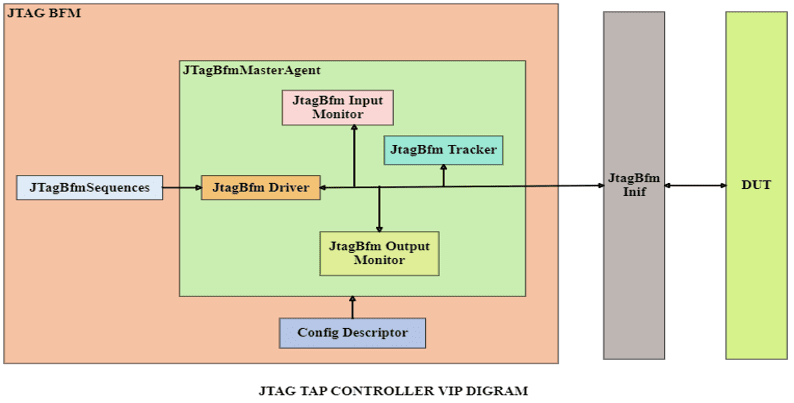

JTAG Tap Controller VIP

Features:

- Error detection and reporting

- Randomized test generation

- Comprehensive Protocol Support

- Functional coverage analysis

- Supports Instruction Register(IR) and Data Register(DR)

- Compatible with a wide range of testbench components such as test generators, sequences and, monitors ensuring comprehensive verification coverage.

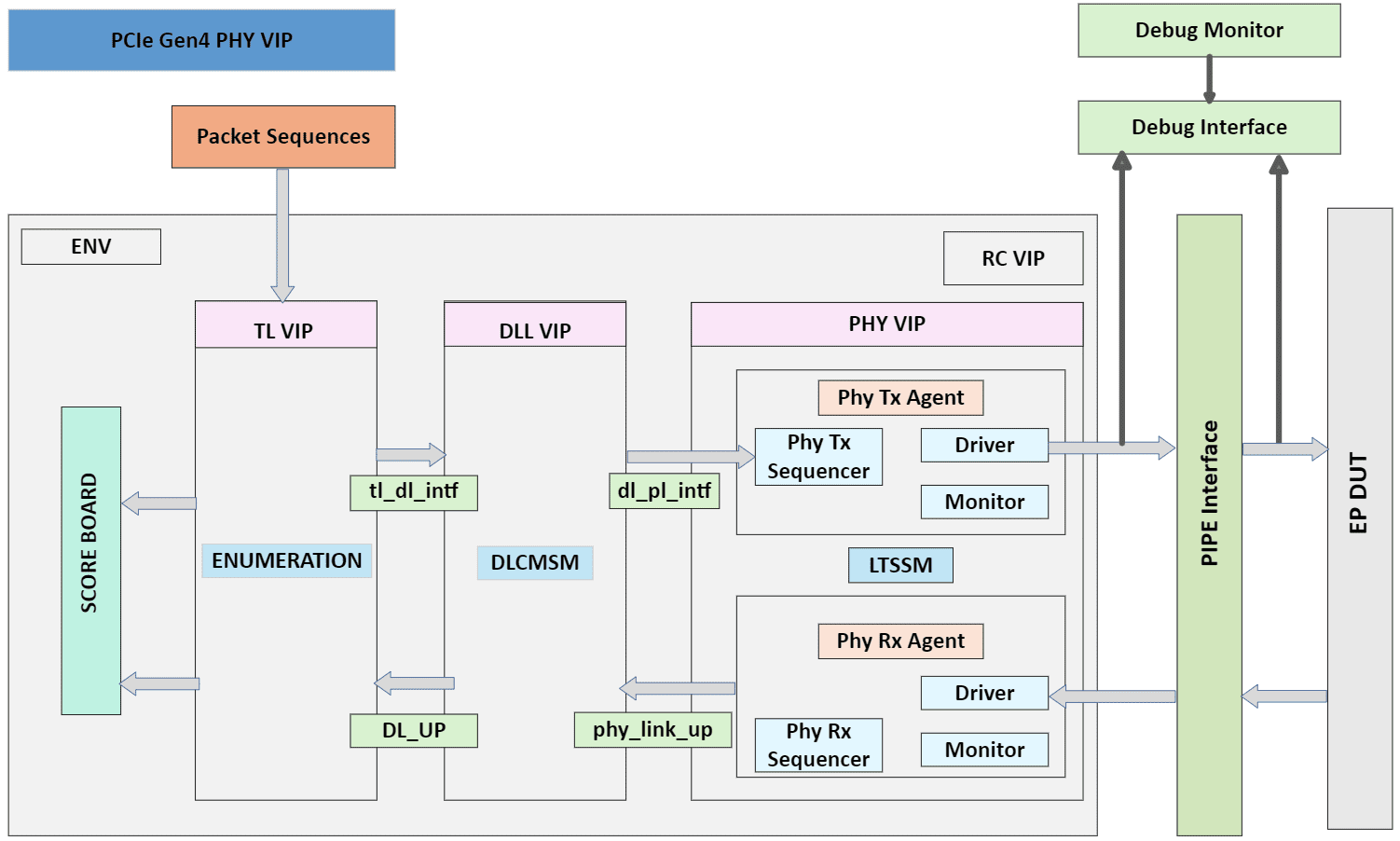

PCIe Gen4 PHY VIP

Features:

- Comprehensiveness: Covers all aspects of the PHY layer, including link training, signal integrity, error detection/correction, equalization and performance under various conditions.

- Configurability: Adapts to different PHY configurations like data width, lane count (including bifurcation), and CTLE settings.

- Automation: Runs tests automatically and reports results for efficient verification.

- Interoperability: Works with various test setups and tools like sequencers, monitors, and scoreboards.

- Extensive lane margining capabilities: Ensures robust signal transmission and reception across different channel conditions.

- Performance analysis under stress: Verifies data integrity and clock recovery under low-supply conditions for reliable operation in demanding environments.

- BIFURCATION support: Validates seamless operation in multi-lane configurations for high-bandwidth applications.

- Compliance verification: Ensures adherence to the PCIe Gen4 specification for interoperability with other compliant devices.

- The specific features and capabilities of the VIP will depend on the chosen vendor and target verification needs.for link layer

- Adapt the VIP configuration to match the specific characteristics and settings of the target PHY IP.

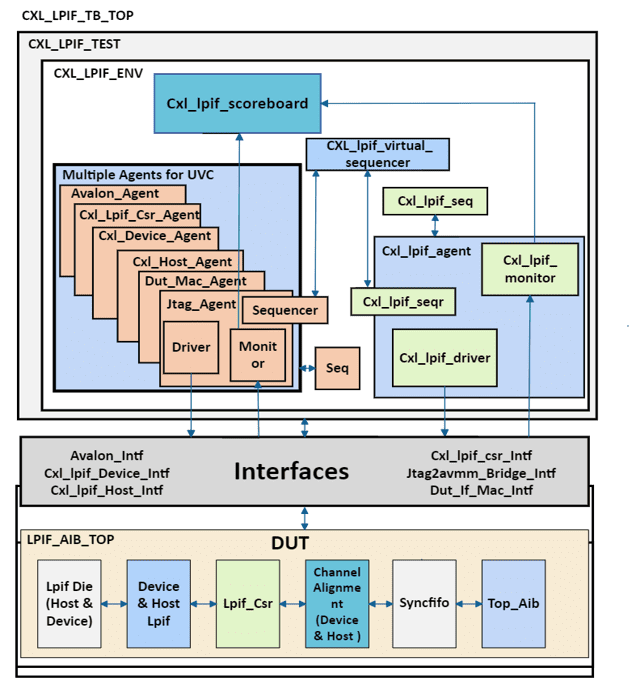

CXL Logical PHY Interface VIP

Features:

- Compile with CXL 2.0, AIB 2.0 and LPIF 1.0 specifications

- AIB Channel count: 1×16

- AIB Interface modes

- Supports x16, x8 and x4 for AIB 2.0

- Lanes for AIB Channel: x1-x4 lanes

- Provides a single link layer port

- AIB modes consists of full, half and quarter rate

- AIB 2.0/Gen2 and AIB 2.0/Gen1

- Support for optional configuration port for link layer

- Configurable mapping of stream ID bits for protocol

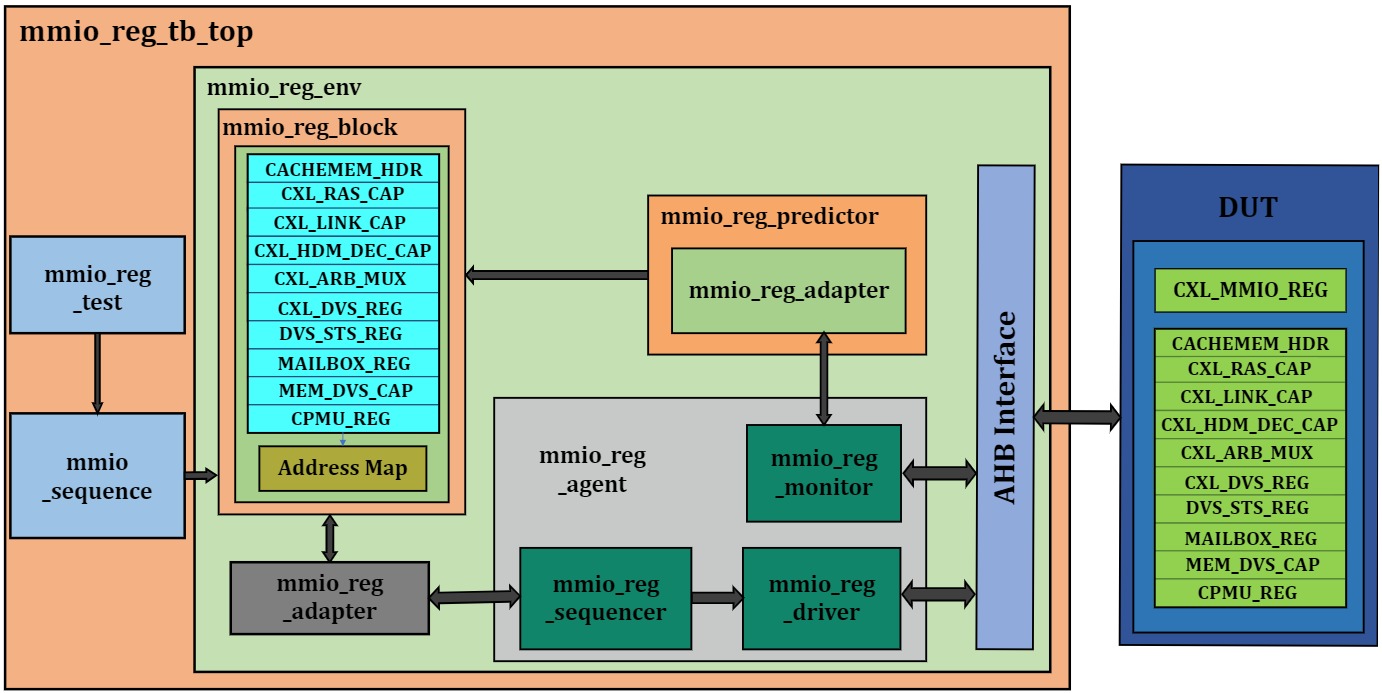

CXL.io MMIO Registers UVM RAL Model

Features:

- CXL 3.0 Compliant with IDE

- Based on PCIe Gen6 64GT/s, Total 16 lanes

- PCIe 4 links of x4 lanes can be configured as 1 x16 or 2 x8

- Vendor-Specific Extended Capability (VSEC) and Designated Vendor-Specific Extended Capability (DVSEC) registers are provided

- AXI-Lite and APB interface for Configuration space register access

- MSI/MSI-X interrupts are supported to indicate the command status.

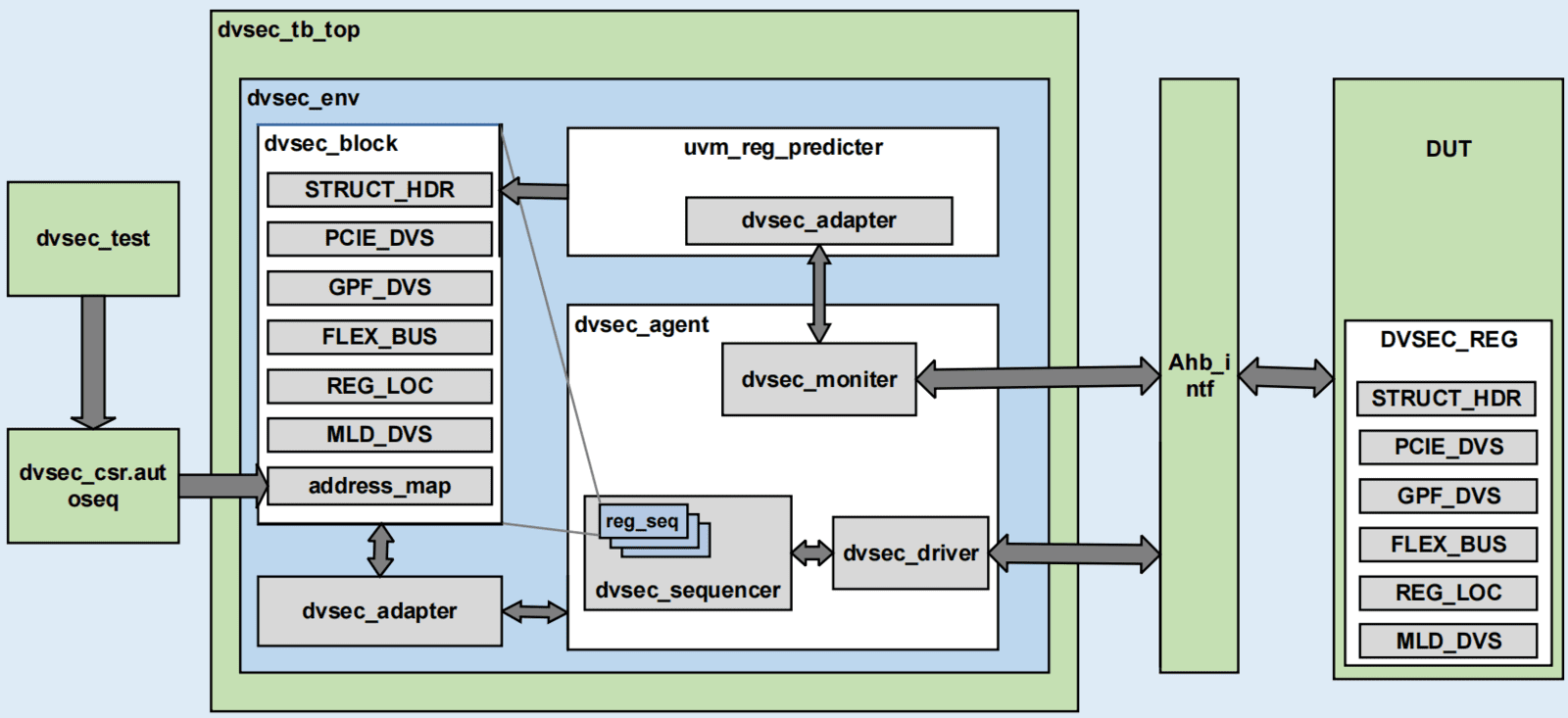

CXL.io DVSEC Registers UVM RAL Model

Features:

- Protocol Compliance: Ensures adherence to CXL standard specifications for accurate representation of CXL_IO DVSEC Registers behavior.

- Register Access and Configuration: Supports read and write operations for seamless access and configuration of CXL_IO DVSEC Registers, handling various register fields.

- Error Handling and Reporting: Incorporates mechanisms for error injection and provides reporting features to analyze and track errors during verification.

- Data Integrity Checks: Implements features for verifying the integrity of data transferred through CXL_IO DVSEC Registers, including error checking as per CXL standard.

- Functional Coverage: Supports functional coverage tracking to ensure comprehensive exercise of all aspects of CXL_IO DVSEC Registers during verification.

- Compliance Testing: Provides built-in tests or scenarios to verify compliance with the CXL standard, ensuring conformity to specified behavior for devices using CXL_IO DVSEC Registers.